Unlocking the Principles and Practicalities of QAM Demodulator Design: A Deep Dive into Techniques, Challenges, and Implementation Strategies

- Introduction to Quadrature Amplitude Modulation (QAM)

- Fundamentals of QAM Demodulation

- Key Components and Architecture of a QAM Demodulator

- Mathematical Foundations and Signal Processing Techniques

- Design Considerations: Performance, Complexity, and Cost

- Implementation Approaches: Analog vs. Digital Demodulators

- Error Detection and Correction in QAM Demodulation

- Common Challenges and Solutions in QAM Demodulator Design

- Testing, Validation, and Performance Metrics

- Applications of QAM Demodulators in Modern Communication Systems

- Future Trends and Advancements in QAM Demodulator Technology

- Conclusion and Best Practices

- Sources & References

Introduction to Quadrature Amplitude Modulation (QAM)

Quadrature Amplitude Modulation (QAM) is a widely used digital modulation technique that conveys data by modulating both the amplitude of two carrier waves, which are out of phase by 90 degrees (in quadrature). This approach enables the transmission of multiple bits per symbol, significantly increasing spectral efficiency compared to simpler modulation schemes. QAM is fundamental in modern communication systems, including digital television, broadband internet, and cellular networks, due to its ability to support high data rates within limited bandwidths.

The design of a QAM demodulator is a critical aspect of any system employing this modulation scheme. The demodulator’s primary function is to accurately recover the transmitted data from the received QAM signal, which may be degraded by noise, interference, and channel impairments. This process involves several key steps: carrier recovery, symbol timing synchronization, and the separation of the in-phase (I) and quadrature (Q) components. Advanced demodulators also incorporate equalization and error correction to mitigate the effects of multipath fading and other distortions.

Recent advancements in digital signal processing and integrated circuit technology have enabled the implementation of highly efficient and robust QAM demodulators, supporting higher-order constellations such as 64-QAM and 256-QAM. These developments are essential for meeting the growing demand for bandwidth-intensive applications. For further technical details and standards, refer to resources from the IEEE and the International Telecommunication Union (ITU).

Fundamentals of QAM Demodulation

Quadrature Amplitude Modulation (QAM) demodulation is a critical process in modern digital communication systems, enabling the extraction of transmitted data from a modulated carrier signal. The fundamental principle of QAM demodulation involves separating the received signal into its in-phase (I) and quadrature (Q) components, which are then used to reconstruct the original digital information. This is typically achieved by mixing the incoming QAM signal with locally generated reference signals—one in phase and one in quadrature (90 degrees out of phase)—followed by low-pass filtering to isolate the baseband signals. The resulting I and Q signals correspond to the amplitude values that represent the transmitted symbol in the QAM constellation diagram.

A key challenge in QAM demodulator design is maintaining synchronization between the receiver’s local oscillator and the incoming carrier, as any phase or frequency offset can lead to symbol misinterpretation. Techniques such as carrier recovery and clock recovery are therefore integral to robust demodulation. Additionally, the demodulator must address channel impairments like noise, fading, and inter-symbol interference, often employing equalization and error correction algorithms to enhance performance. The complexity of the demodulator increases with higher-order QAM schemes, as the constellation becomes denser and more susceptible to errors.

Modern QAM demodulators are implemented using digital signal processing (DSP) techniques, allowing for adaptive filtering, automatic gain control, and real-time error correction. These advancements have enabled QAM to be widely adopted in applications such as broadband wireless, cable television, and high-speed data modems, as detailed by the International Telecommunication Union and IEEE.

Key Components and Architecture of a QAM Demodulator

The architecture of a Quadrature Amplitude Modulation (QAM) demodulator is defined by several key components, each playing a critical role in accurately recovering the transmitted data from a modulated carrier. At the front end, the analog front-end (AFE) typically includes a low-noise amplifier (LNA) and an anti-aliasing filter to condition the received signal and suppress out-of-band noise. The conditioned signal is then digitized by a high-speed analog-to-digital converter (ADC), which must provide sufficient resolution and sampling rate to preserve the integrity of the QAM constellation.

Following digitization, the downconversion stage employs digital mixers and numerically controlled oscillators (NCOs) to shift the signal to baseband, producing in-phase (I) and quadrature (Q) components. These components are then processed by matched filters or pulse-shaping filters, such as root-raised cosine filters, to maximize signal-to-noise ratio and minimize intersymbol interference.

A critical block in the architecture is the carrier recovery loop, often implemented as a phase-locked loop (PLL) or a Costas loop, which synchronizes the local oscillator with the received carrier frequency and phase. In parallel, a timing recovery circuit ensures accurate symbol timing, often using algorithms like Gardner or Mueller and Müller. The equalizer compensates for channel-induced distortions, such as multipath fading, using adaptive algorithms.

Finally, the symbol decision block maps the filtered and synchronized I/Q samples to the nearest constellation points, reconstructing the transmitted data. Modern QAM demodulators often integrate these functions in digital signal processors or FPGAs for flexibility and performance, as detailed by Analog Devices and Texas Instruments.

Mathematical Foundations and Signal Processing Techniques

The design of a Quadrature Amplitude Modulation (QAM) demodulator is fundamentally rooted in mathematical signal processing principles, particularly those involving orthogonal signal decomposition and complex baseband representation. QAM signals are characterized by the simultaneous modulation of two carrier waves, typically sine and cosine, which are orthogonal to each other. This orthogonality allows the in-phase (I) and quadrature (Q) components to be separated and independently processed at the receiver. The demodulation process begins with coherent detection, where the received signal is mixed with locally generated reference carriers matched in frequency and phase to the transmitter. This operation yields the I and Q baseband signals, which are then low-pass filtered to remove high-frequency components introduced during mixing.

Mathematically, the received QAM signal can be expressed as a linear combination of the I and Q components, each multiplied by their respective carrier functions. The demodulator employs matched filtering or correlation techniques to maximize the signal-to-noise ratio (SNR) and minimize inter-symbol interference (ISI). Symbol synchronization and carrier recovery algorithms are crucial to ensure accurate extraction of the transmitted symbols, as any phase or frequency offset can lead to symbol misinterpretation. Advanced signal processing techniques, such as adaptive equalization, are often integrated to mitigate channel impairments like multipath fading and noise. The overall performance of a QAM demodulator is thus highly dependent on the precision of these mathematical and signal processing operations, as detailed in standards and technical literature from organizations such as the IEEE and ITU.

Design Considerations: Performance, Complexity, and Cost

When designing a Quadrature Amplitude Modulation (QAM) demodulator, engineers must carefully balance performance, complexity, and cost to meet system requirements. Performance considerations include bit error rate (BER), signal-to-noise ratio (SNR), and the ability to handle channel impairments such as phase noise, frequency offset, and multipath fading. High-order QAM schemes (e.g., 64-QAM, 256-QAM) offer increased spectral efficiency but demand more precise demodulation and are more susceptible to noise and distortion, necessitating advanced equalization and error correction techniques International Telecommunication Union.

Complexity is driven by the choice of algorithms for carrier recovery, symbol timing synchronization, and channel equalization. Implementing coherent demodulation, which is essential for higher-order QAM, requires sophisticated digital signal processing (DSP) and often increases hardware resource usage and power consumption. Designers must decide between analog and digital architectures, with digital solutions offering flexibility and scalability at the expense of increased computational requirements IEEE.

Cost considerations encompass both the bill of materials (BOM) and development expenses. While high-performance demodulators may use field-programmable gate arrays (FPGAs) or application-specific integrated circuits (ASICs), these solutions can be expensive. Alternatively, lower-cost microcontroller-based designs may suffice for lower-order QAM or less demanding applications. Ultimately, the optimal QAM demodulator design is a trade-off, tailored to the target application’s bandwidth, power, and economic constraints European Telecommunications Standards Institute.

Implementation Approaches: Analog vs. Digital Demodulators

The implementation of Quadrature Amplitude Modulation (QAM) demodulators can be broadly categorized into analog and digital approaches, each with distinct advantages and trade-offs. Analog QAM demodulators traditionally employ mixers, local oscillators, and analog filters to extract the in-phase (I) and quadrature (Q) components from the received signal. These circuits are valued for their low latency and real-time processing capabilities, making them suitable for high-frequency applications where digital processing may be limited by sampling rates or power constraints. However, analog designs are susceptible to component tolerances, temperature drift, and non-linearities, which can degrade demodulation accuracy and require frequent calibration Analog Devices.

In contrast, digital QAM demodulators leverage high-speed analog-to-digital converters (ADCs) to sample the incoming signal, followed by digital signal processing (DSP) algorithms to perform carrier recovery, symbol timing, and demodulation. Digital implementations offer superior flexibility, allowing for adaptive equalization, error correction, and reconfigurability through software updates. They also provide greater immunity to analog impairments and facilitate integration with modern communication systems-on-chip (SoCs) Texas Instruments. However, digital demodulators require significant computational resources and power, especially at higher symbol rates, and their performance is constrained by ADC resolution and sampling speed.

The choice between analog and digital QAM demodulator architectures depends on system requirements such as bandwidth, power consumption, integration level, and cost. Hybrid approaches, combining analog front-ends with digital back-ends, are increasingly common in modern receivers to balance performance and efficiency National Instruments.

Error Detection and Correction in QAM Demodulation

Error detection and correction are critical components in the design of Quadrature Amplitude Modulation (QAM) demodulators, as they ensure reliable data recovery in the presence of noise, interference, and channel impairments. In practical QAM systems, transmitted symbols are susceptible to errors due to additive white Gaussian noise (AWGN), phase noise, and multipath fading. To mitigate these effects, QAM demodulators often incorporate forward error correction (FEC) schemes such as convolutional codes, Reed-Solomon codes, or low-density parity-check (LDPC) codes. These codes add redundancy to the transmitted data, enabling the receiver to detect and correct a certain number of errors without retransmission.

At the demodulator, the received signal is first mapped to the nearest constellation point, a process known as symbol decision. The demodulated bitstream is then passed through an error detection and correction module. For instance, cyclic redundancy check (CRC) codes are commonly used for error detection, while FEC codes handle correction. The integration of soft-decision decoding, where the demodulator provides likelihood information (rather than hard binary decisions), further enhances error correction performance, especially in high-order QAM systems where symbol spacing is reduced and error probability increases.

The choice of error correction technique and its implementation complexity are influenced by the target bit error rate (BER), system latency requirements, and available processing resources. Modern communication standards, such as those defined by the European Telecommunications Standards Institute and International Telecommunication Union, specify robust error correction frameworks for QAM-based systems, ensuring high data integrity even under challenging channel conditions.

Common Challenges and Solutions in QAM Demodulator Design

Designing a Quadrature Amplitude Modulation (QAM) demodulator presents several technical challenges that can significantly impact system performance. One of the primary issues is carrier synchronization. QAM demodulators require precise alignment with the carrier frequency and phase; any offset can cause constellation rotation, leading to symbol errors. Solutions include implementing robust carrier recovery loops, such as phase-locked loops (PLLs), and employing pilot symbols for reference, as recommended by International Telecommunication Union (ITU) standards.

Another challenge is timing synchronization. Accurate symbol timing is crucial to avoid inter-symbol interference (ISI). Techniques like Gardner or Mueller and Müller timing error detectors are commonly used to maintain optimal sampling points, as detailed by IEEE publications. Additionally, channel impairments such as multipath fading, noise, and phase noise can distort the received signal. Adaptive equalization algorithms, including least mean squares (LMS) and decision feedback equalizers (DFE), are effective in mitigating these effects.

Nonlinearities in the analog front-end, such as amplifier distortion, can also degrade demodulation accuracy. Careful analog design and digital compensation techniques are necessary to address these issues. Finally, complexity and power consumption are significant concerns, especially in portable or high-throughput applications. Designers often employ hardware-efficient architectures and fixed-point arithmetic to balance performance and resource usage, as outlined by European Telecommunications Standards Institute (ETSI) guidelines.

In summary, overcoming these challenges requires a combination of advanced signal processing algorithms, robust synchronization schemes, and efficient hardware implementation to ensure reliable QAM demodulation in practical communication systems.

Testing, Validation, and Performance Metrics

Testing, validation, and performance evaluation are critical phases in the design of a Quadrature Amplitude Modulation (QAM) demodulator, ensuring that the system meets both theoretical and practical requirements. The testing process typically begins with simulation-based verification, where the demodulator is subjected to a variety of channel conditions, including additive white Gaussian noise (AWGN), multipath fading, and phase noise. These simulations help identify the bit error rate (BER) performance across different signal-to-noise ratios (SNR), which is a primary metric for assessing demodulator robustness and efficiency. Hardware-in-the-loop (HIL) testing and prototyping on platforms such as FPGAs or DSPs further validate the design under real-time constraints and hardware imperfections.

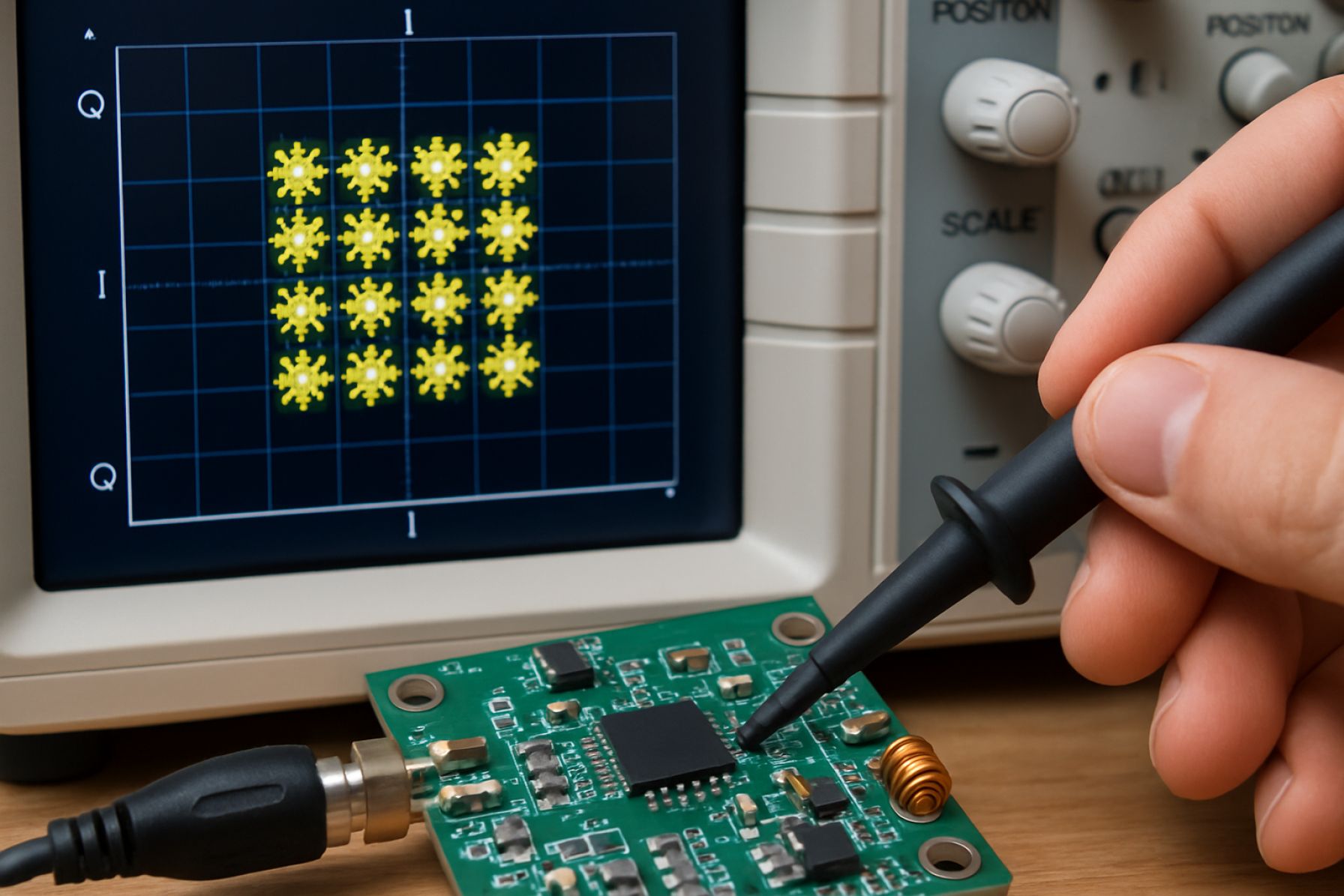

Validation also involves compliance with relevant communication standards, such as those defined by the International Telecommunication Union and the Institute of Electrical and Electronics Engineers. These standards specify acceptable error rates, spectral efficiency, and interoperability requirements. Performance metrics extend beyond BER to include symbol error rate (SER), error vector magnitude (EVM), and computational complexity. EVM, in particular, quantifies the deviation of the received signal constellation from the ideal, serving as a sensitive indicator of demodulator fidelity and implementation quality.

Comprehensive testing and validation not only ensure that the QAM demodulator performs reliably under diverse conditions but also facilitate optimization for power consumption, latency, and hardware resource utilization. This systematic approach is essential for deploying QAM demodulators in modern communication systems, where high data rates and robust performance are paramount.

Applications of QAM Demodulators in Modern Communication Systems

Quadrature Amplitude Modulation (QAM) demodulators are integral to the performance and efficiency of modern communication systems, enabling high data rate transmission over limited bandwidth channels. Their applications span a wide range of technologies, including digital television broadcasting, broadband internet access, cellular networks, and optical fiber communications. In digital cable and satellite television, QAM demodulators decode complex signal constellations to deliver high-definition video and audio content efficiently, supporting standards such as DVB-C and ATSC. Similarly, in broadband internet, cable modems utilize QAM demodulation to achieve high-speed data transfer over coaxial infrastructure, as specified by the CableLabs DOCSIS standards.

In wireless communications, QAM demodulators are fundamental to 4G LTE and 5G NR systems, where adaptive modulation schemes dynamically select QAM orders (e.g., 16-QAM, 64-QAM, 256-QAM) based on channel conditions to maximize spectral efficiency and throughput. This adaptability is crucial for meeting the demands of mobile broadband and IoT applications, as outlined by the 3rd Generation Partnership Project (3GPP). Furthermore, in optical fiber networks, advanced QAM demodulation techniques enable coherent detection, supporting terabit-level data rates and long-haul transmission with minimal signal degradation, as described by the International Telecommunication Union (ITU).

The widespread adoption of QAM demodulators in these domains underscores their critical role in achieving reliable, high-capacity, and flexible communication infrastructures, driving the evolution of global connectivity.

Future Trends and Advancements in QAM Demodulator Technology

The evolution of Quadrature Amplitude Modulation (QAM) demodulator technology is being shaped by the increasing demand for higher data rates, spectral efficiency, and robust performance in next-generation communication systems. One significant trend is the integration of machine learning algorithms into QAM demodulators, enabling adaptive equalization and improved symbol detection in the presence of channel impairments such as noise, fading, and interference. These intelligent demodulators can dynamically adjust their parameters in real time, optimizing performance for varying channel conditions and supporting higher-order QAM constellations, such as 1024-QAM and beyond, which are essential for 5G and future 6G networks (International Telecommunication Union).

Another advancement is the development of low-power, high-speed digital signal processing (DSP) architectures tailored for QAM demodulation. These architectures leverage parallel processing and advanced hardware accelerators, such as field-programmable gate arrays (FPGAs) and application-specific integrated circuits (ASICs), to achieve real-time demodulation with minimal latency and power consumption (IEEE). Additionally, the adoption of software-defined radio (SDR) platforms allows for flexible and reconfigurable QAM demodulator implementations, facilitating rapid prototyping and deployment of new modulation schemes as standards evolve.

Looking forward, the convergence of quantum computing and advanced error correction techniques may further enhance QAM demodulator performance, enabling ultra-reliable and high-capacity wireless links. As communication systems continue to evolve, QAM demodulator design will remain at the forefront of innovation, driving the capabilities of future wireless and optical networks (European Telecommunications Standards Institute).

Conclusion and Best Practices

In conclusion, the design of Quadrature Amplitude Modulation (QAM) demodulators is a critical aspect of modern digital communication systems, directly impacting data throughput, spectral efficiency, and system robustness. Effective QAM demodulator design requires careful consideration of synchronization, carrier recovery, and adaptive equalization to mitigate channel impairments such as noise, fading, and inter-symbol interference. Implementing advanced algorithms for timing and phase recovery, such as Costas loops and decision-directed methods, enhances demodulation accuracy and system resilience IEEE.

Best practices in QAM demodulator design include thorough simulation and hardware-in-the-loop testing to validate performance under realistic channel conditions. Designers should prioritize low-latency architectures and efficient digital signal processing (DSP) implementations to meet the demands of high-speed communication standards. Additionally, leveraging error correction codes and adaptive modulation schemes can further improve reliability and adaptability in dynamic environments International Telecommunication Union (ITU).

It is also essential to maintain flexibility in the demodulator architecture to support various QAM constellations (e.g., 16-QAM, 64-QAM, 256-QAM), enabling scalability for future system upgrades. Regularly updating design methodologies in line with emerging standards and leveraging open-source tools and reference designs can accelerate development and ensure compliance with industry requirements European Telecommunications Standards Institute (ETSI). By adhering to these best practices, engineers can achieve robust, efficient, and future-proof QAM demodulator designs suitable for a wide range of applications.

Sources & References

- IEEE

- International Telecommunication Union (ITU)

- Texas Instruments

- National Instruments

- CableLabs DOCSIS

- 3rd Generation Partnership Project (3GPP)